M-Labs Github . Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. Follow their code on github.

from grafana.com

Installing via conda [deprecated] upgrading artiq. A python toolbox for building complex digital hardware. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Despite being faster than schematics entry, hardware design with verilog and vhdl. Follow their code on github.

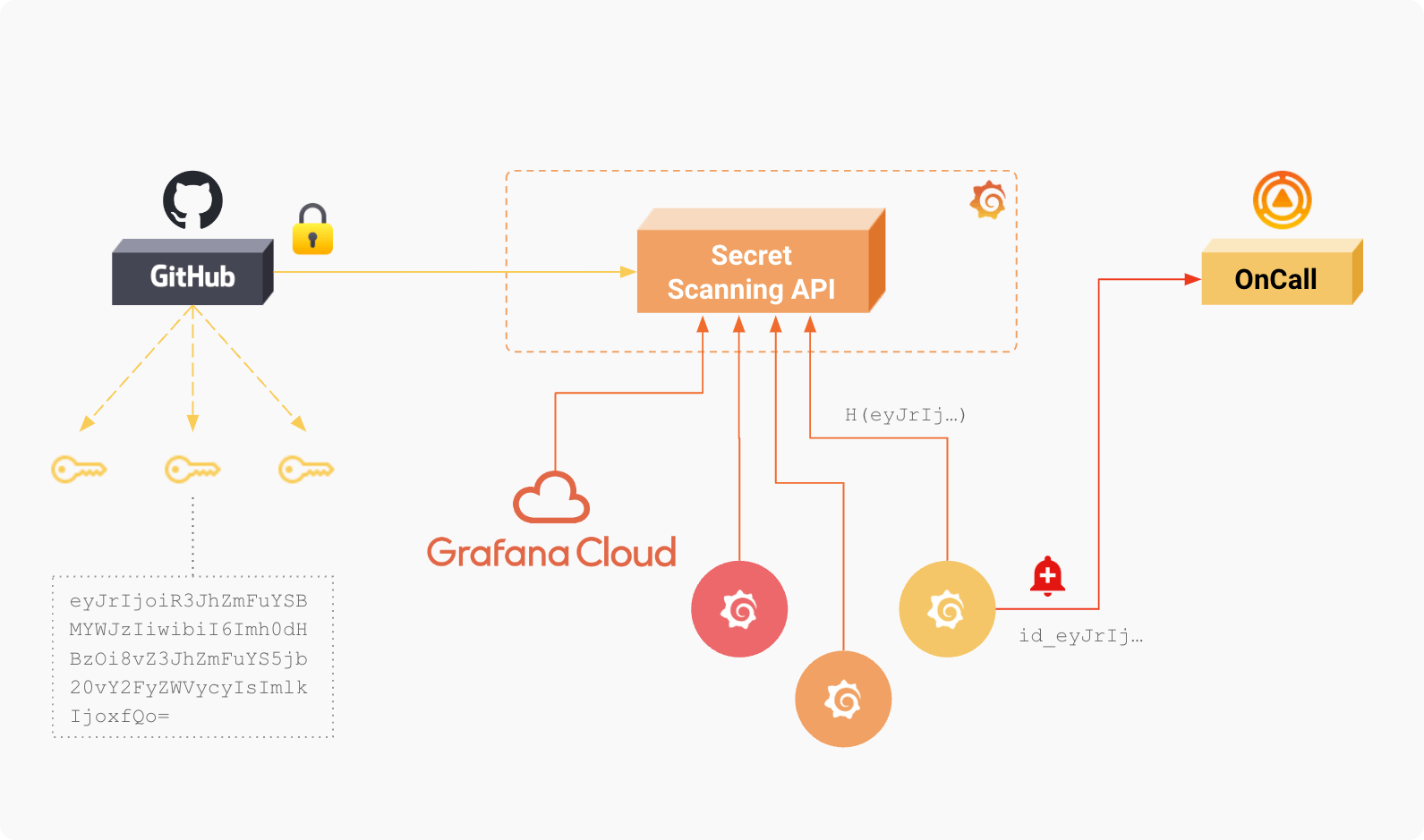

Grafana Labs partners with GitHub to enable secret scanning Grafana Labs

M-Labs Github Despite being faster than schematics entry, hardware design with verilog and vhdl. Despite being faster than schematics entry, hardware design with verilog and vhdl. A python toolbox for building complex digital hardware. Follow their code on github. Installing via conda [deprecated] upgrading artiq. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient.

From architizer.com

mLab by Arup Architizer M-Labs Github Despite being faster than schematics entry, hardware design with verilog and vhdl. Follow their code on github. Installing via conda [deprecated] upgrading artiq. A python toolbox for building complex digital hardware. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From github.com

GitHub KrishnamohanYerrabilli/Deploying_Java_Responsive_Website_on M-Labs Github Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. Follow their code on github. Installing via conda [deprecated] upgrading artiq. M-Labs Github.

From www.facebook.com

MLab Chéhim M-Labs Github Follow their code on github. Despite being faster than schematics entry, hardware design with verilog and vhdl. Installing via conda [deprecated] upgrading artiq. A python toolbox for building complex digital hardware. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From svitla.com

GitLab vs GitHub Detailed Overview with Key Differences M-Labs Github Installing via conda [deprecated] upgrading artiq. A python toolbox for building complex digital hardware. Follow their code on github. Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From marketinglab.com

About M_LAB M-Labs Github Despite being faster than schematics entry, hardware design with verilog and vhdl. A python toolbox for building complex digital hardware. Follow their code on github. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Installing via conda [deprecated] upgrading artiq. M-Labs Github.

From github.com

An introduction to GitHub Copilot · community · Discussion 39086 · GitHub M-Labs Github A python toolbox for building complex digital hardware. Despite being faster than schematics entry, hardware design with verilog and vhdl. Follow their code on github. Installing via conda [deprecated] upgrading artiq. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From grafana.com

Grafana Labs partners with GitHub to enable secret scanning Grafana Labs M-Labs Github Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Follow their code on github. Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. A python toolbox for building complex digital hardware. M-Labs Github.

From www.youtube.com

Discovering the AGG World MLabs & PSHA's Groundbreaking Research M-Labs Github Follow their code on github. A python toolbox for building complex digital hardware. Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Installing via conda [deprecated] upgrading artiq. M-Labs Github.

From www.tabnews.com.br

GitHub Learning Lab será encerrado · gpoleszuk · TabNews M-Labs Github Follow their code on github. A python toolbox for building complex digital hardware. Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From www.youtube.com

Git integration and Version Control for Jupyter Notebooks in Noteable M-Labs Github Installing via conda [deprecated] upgrading artiq. Follow their code on github. Despite being faster than schematics entry, hardware design with verilog and vhdl. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. M-Labs Github.

From byuistats.github.io

R Lab M-Labs Github Installing via conda [deprecated] upgrading artiq. Follow their code on github. Despite being faster than schematics entry, hardware design with verilog and vhdl. A python toolbox for building complex digital hardware. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From blog.reviewnb.com

How to use the JupyterLab Git extension ReviewNB Blog M-Labs Github A python toolbox for building complex digital hardware. Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. Follow their code on github. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. M-Labs Github.

From www.facebook.com

m.lab_official Home M-Labs Github Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Follow their code on github. A python toolbox for building complex digital hardware. Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. M-Labs Github.

From techcommunity.microsoft.com

GitHub Copilot Labs A Game Changer for New Student Coders M-Labs Github Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. Installing via conda [deprecated] upgrading artiq. Follow their code on github. Despite being faster than schematics entry, hardware design with verilog and vhdl. M-Labs Github.

From techcommunity.microsoft.com

GitHub Copilot Labs A Game Changer for New Student Coders M-Labs Github Despite being faster than schematics entry, hardware design with verilog and vhdl. Installing via conda [deprecated] upgrading artiq. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Follow their code on github. A python toolbox for building complex digital hardware. M-Labs Github.

From www.amazon.com

S&M Labs M-Labs Github Installing via conda [deprecated] upgrading artiq. Follow their code on github. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. Despite being faster than schematics entry, hardware design with verilog and vhdl. M-Labs Github.

From github.com

elevenlabs · GitHub Topics · GitHub M-Labs Github Follow their code on github. Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. A python toolbox for building complex digital hardware. Installing via conda [deprecated] upgrading artiq. Despite being faster than schematics entry, hardware design with verilog and vhdl. M-Labs Github.

From docs.saucelabs.com

saucectl with GitHub Actions Sauce Labs Documentation M-Labs Github Traditional gateware design with verilog and vhdl is well known to be tedious and inefficient. Despite being faster than schematics entry, hardware design with verilog and vhdl. Follow their code on github. Installing via conda [deprecated] upgrading artiq. A python toolbox for building complex digital hardware. M-Labs Github.